При аппаратной реализации вычислений числа могут быть представлены в форматах с фиксированной или с плавающей запятой. Вычислительные устройства, работающие в формате с фиксированной запятой, менее требовательны к объему аппаратных ресурсов. Однако вычисления в формате с фиксированной запятой не всегда могут обеспечить достаточную точность, а также подвержены влиянию эффектов конечной разрядности. Формат с плавающей запятой более устойчив к сбоям и дает высокую точность вычислений, но его применение сопровождается большим расходом аппаратных ресурсов и (или) снижением скорости вычислений.

Наиболее востребованным среди арифметических устройств является сумматор (вычитатель), который используют, например, до 50 % устройств цифровой обработки сигналов (ЦОС). Вместе с тем, суммирование в формате с плавающей запятой наиболее сложно для реализации [1].

При реализации вычислений на микроконтроллерах или сигнальных процессорах оптимизация операции сложения, равно как и других операций, выполняется производителем элементной базы. В тех случаях, когда вычисления реализуются на ПЛИС архитектуры FPGA, оптимизация выполняемых операций является задачей разработчика. Целями оптимизации, как правило, являются:

– достижение максимальной производительности (рабочей частоты) устройства;

– минимизация латентности (задержки появления результатов вычислений относительно момента поступления исходных данных);

– минимизация ресурсоемкости устройства.

В данной статье рассмотрено, каким образом можно реализовать сложение в формате с плавающей запятой на современных FPGA и исследовано влияние на достижение перечисленных выше целей таких факторов, как используемые ресурсы FPGA и латентность сумматоров.

Ресурсы FPGA, пригодные для реализации сумматоров. Операция сложения в формате с плавающей запятой может быть реализована на FPGA в двух вариантах: с использованием исключительно ресурсов программируемой логики или с привлечением блоков цифровой обработки сигналов (ЦОС).

При реализации сумматоров на программируемой логике важную роль в ускорении вычислений играют цепи переноса (carry logic), находящиеся в конфигурируемых логических блоках FPGA. Кроме того, требуется большое количество табличных преобразователей (LUT).

Ожидаемым преимуществом использования ЦОС-блоков является компактность размещения элементов сумматора на FPGA, а также более высокая производительность за счет выделенных логических и трассировочных ресурсов. Однако нужно учитывать, что в современных FPGA, за исключением [2], ЦОС-блоки ориентированы на вычисления в формате с фиксированной запятой. Работа в формате с плавающей запятой возможна, но требует использования наряду с ЦОС-блоками программируемой логики.

Способы описания и инструменты проектирования сумматоров. Для выполнения исследования выбрана FPGA XC7A200T-3 фирмы Xilinx. Проектирование сумматоров выполнялось в среде ISE Design Suite 14.7.

Производительность, ресурсоемкость и другие характеристики вычислительных устройств, работающих в формате с плавающей запятой, во многом зависят от способа их описания. В [3] отмечается, что одним из наиболее эффективных способов исходного описания подобных устройств является использование настраиваемых модулей интеллектуальной собственности Floating Point Operator и инструмента Core Generator. Такой способ описания выбран и в данной работе.

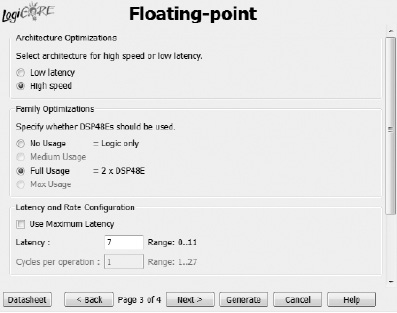

Кроме того, Core Generator предоставляет графический интерфейс для настройки параметров модуля интеллектуальной собственности, в том числе для указания используемых ресурсов FPGA и латентности сумматоров, выраженной в количестве тактовых импульсов (рисунок).

Сумматоры, рассмотренные в данной работе, рассчитаны на числа, представленные в соответствии со стандартом IEEE 754: для знака числа отводится 1 разряд, для экспоненты – 8 разрядов, для мантиссы – 23 разряда без учета целой части.

Чтобы временной анализатор среды ISE Design Suite выполнил оценку производительности проектируемого устройства, необходимо наложить на него временные ограничения [4]. Максимальной производительностью реализованных на ПЛИС устройств является производительность отдельных логических ресурсов (конфигурируемых логических блоков, блоков ЦОС). При выполнении исследования на проекты сумматоров накладывалось временное ограничение PERIOD, куда в качестве периода тактового сигнала подставлялись значения, взятые из [5].

Результаты оценки производительности и ресурсоемкости сумматоров при различных настройках оценивались по итогам размещения и трассировки соответствующих проектов с помощью инструмента PlanAhead.

Результаты исследований и их обсуждение. В табл. 1 и 2 приведены результаты реализации сумматоров исключительно на программируемой логике FPGA и с использованием блоков ЦОС при различных настройках латентности. В таблицах показаны результаты оценки производительности (максимальной тактовой частоты fmax) сумматоров, а также требуемое для их реализации количество D-триггеров (FF) и табличных преобразователей (LUT). Количество блоков ЦОС не показано в таблице 2, так как в рамках исследования требовалось 2 блока при любых настройках латентности.

Из табл. 1 следует, что повышение латентности сумматора, реализованного на программируемой логике FPGA, сопровождается повышением его максимальной тактовой частоты fmax. Однако если выразить латентность в единицах измерения времени, подставив при расчетах полученные значения fmax, будет очевидно, что достигнутый прирост производительности не оправдывает дополнительного расхода триггеров, так как абсолютное время выполнения сложения с повышением количества тактов увеличивается. В целом можно отметить, что производительность сумматоров заметно ниже предельной производительности отдельных конфигурируемых логических блоков FPGA [5]. В первую очередь это связано с неизбежными задержками распространения сигналов на программируемых соединениях FPGA. Однако потери производительности могут быть связаны и с тем, что Floating Point Operator не является специализированным средством для реализации сумматоров. Отдельные операции, выполняемые при суммировании в формате с плавающей запятой, могут быть реализованы не оптимально.

Настройки модуля Floating Point Operator

Таблица 1

Результаты реализации сумматоров на программируемой логике FPGA

|

Латентность (такт. импульсов) |

2 |

4 |

6 |

8 |

10 |

12 |

|

fmax, МГц |

147 |

267 |

356 |

331 |

476 |

452 |

|

LUT |

417 |

387 |

356 |

379 |

379 |

389 |

|

FF |

73 |

181 |

275 |

394 |

474 |

541 |

Таблица 2

Результаты реализации сумматоров с использованием блоков ЦОС FPGA

|

Латентность (такт. импульсов) |

1 |

3 |

5 |

7 |

9 |

11 |

|

fmax, МГц |

628 |

155 |

195 |

218 |

334 |

366 |

|

LUT |

185 |

237 |

212 |

223 |

211 |

209 |

|

FF |

32 |

74 |

127 |

228 |

264 |

319 |

Из табл. 2 следует, что при использовании блоков ЦОС для реализации сумматора наилучшие показатели производительности и ресурсоемкости обеспечивает латентность, равная одному такту. Повышение латентности приводит к спаду производительности, который можно объяснить увеличением доли программируемой логики в составе сумматора и усложнением его размещения и трассировки. Данные, представленные в табл. 2, позволяют также заключить, что использование блоков ЦОС значительно сокращает требуемый объем триггеров и табличных преобразователей.

Заключение

На основе результатов, представленных в табл. 1 и 2, можно заключить, что в большинстве случаев предпочтительным способом реализации на FPGA операции арифметического сложения в формате с плавающей запятой является использование блоков ЦОС. В случае использования ресурсов программируемой логики устанавливать высокую латентность сумматора имеет смысл, если от устройства, в состав которого он входит, требуется высокая частота обработки данных.

science-review.ru

science-review.ru